Product Summary

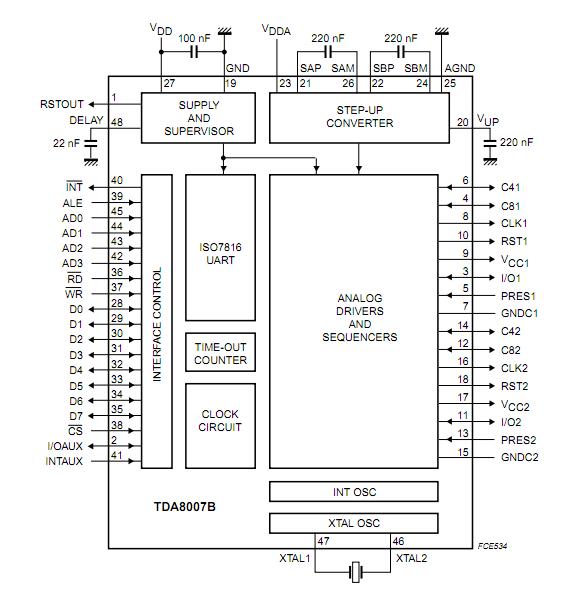

The TDA8007BHL is a low cost card interface for dual smart card readers. Controlled through a parallel bus, it takes care of all ISO 7816, EMV and GSM11-11 requirements. It may be interfaced to the P0/P2 ports of a 80C51 family microcontroller, and be addressed as a memory through MOVX instructions. It may also be addressed on a non-multiplexed 8-bit data bus, by means of address registers AD0, AD1, AD2 and AD3. The applications of the TDA8007BHL include Multiple smart card readers for multiprotocol applications (EMV banking, digital pay TV, access control, etc.).

Parametrics

TDA8007BHL absolute maximum ratings: (1)VDDA analog supply voltage: -0.5 to +6.5 V; (2)VDD supply voltage: -0.5 to +6.5 V; (3)Vn input voltage on all pins except S1, S2, S3, S4 and VUP: -0.5 to VDD + 0.5 V; input voltage on pins S1, S2, S3, S4 and VUP: -0.5 to +7.5 V; (4)In1 DC current into all pins except S1, S2, S3, S4 and VUP: -5 to +5 mA; (5)In3 DC current from or to pins S1, S2, S3, S4 and VUP: -200 to +200 mA; (6)Ptot total power dissipation Tamb = -20 to +85℃: 700 mW; (7)Tstg IC storage temperature: -55 to +150℃; (8)Tj, junction temperature: 125℃.

Features

TDA8007BHL features: (1)Control and communication through an 8-bit parallel interface, compatible with multiplexed or non-multiplexed memory access; (2)Specific ISO UART with parallel access on I/O for automatic convention processing, variable baud rate through frequency or division ratio programming, error management at character level for T = 0, extra guard time register; (3)1 to 8 characters FIFO in reception mode; (4)Parity error counter in reception mode; (5)Dual VCC generation (5 V ±5%, 65 mA (max.) or 3 V ±8%, 50 mA (max.) with controlled rise and fall times); (6)Dual cards clock generation (up to 10 MHz), with two times synchronous frequency doubling; (7)Cards clock STOP HIGH, clock STOP LOW or 1.25 MHz (from internal oscillator) for cards Power-down mode; (8)Automatic activation and deactivation sequence through an independent sequencer; (9)Supports the asynchronous protocols T = 0 and T = 1 in accordance with ISO 7816 and EMV; (10)Versatile 24-bit time-out counter for Answer To Reset (ATR) and waiting times processing; (11)22 Elementary Time Unit (ETU) counter for Block Guard Time (BGT).

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

TDA8007BHL/C2,118 |

NXP Semiconductors |

I/O Controller Interface IC SMART CARD INTERFACE |

Data Sheet |

Negotiable |

|

||||||||||||

|

TDA8007BHL/C3,118 |

NXP Semiconductors |

I/O Controller Interface IC INTERFACE CARD MP |

Data Sheet |

|

|

||||||||||||

|

TDA8007BHL/C4,118 |

NXP Semiconductors |

I/O Controller Interface IC 12bit 2-I/Os 5V |

Data Sheet |

|

|

||||||||||||

|

TDA8007BHLB-T |

NXP Semiconductors |

I/O Controller Interface IC SMART CARD INTERFACE 2 SLOTS |

Data Sheet |

Negotiable |

|

||||||||||||

(Hong Kong)

(Hong Kong)